|

AES-128

1.0

Fully Unrolled VHDL Implementation of AES-128

|

|

AES-128

1.0

Fully Unrolled VHDL Implementation of AES-128

|

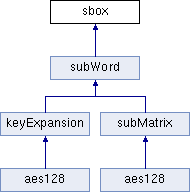

AES S-box. More...

Entities | |

| Canright | architecture |

| Behavioral architecture of the Canright AES S-box. More... | |

| Lut | architecture |

| AES S-box implementation based on a look-up table. More... | |

Libraries | |

| IEEE | |

| work | |

Use Clauses | |

| IEEE.std_logic_1164.all | |

| IEEE.numeric_std.all | |

| work.aes128Pkg.all | |

Ports | |

| In_DI | in Byte |

| Input to the S-box. | |

| Out_DO | out Byte |

| Substituted output of the S-box. | |

AES S-box.

AES S-box implementation based on the approach by D. Canright [1].

The present design implements the S-box of the Advanced Encryption Standard (AES). Since the overall AES structure is based on a byte-oriented design, also the S-box hast been implemented such that a single byte can be substituted. This S-box was realized using a "straight-forward" approach using a LUT based on an array of constants. Thereby shifting all the "effort" of the actual architecture over to the synthesizer.

AES S-box implementation based on the approach by D. Canright, which uses the subfields GF(2^2) and GF(2^4) in order to realize the field inversion in GF(2^8). Thereby the area footprint of the resulting architecture should be significantly smaller than the LUT-based approach using only a constant array and shifting the effort of the actual implementation over to the synthesizer.