|

AES-128

1.0

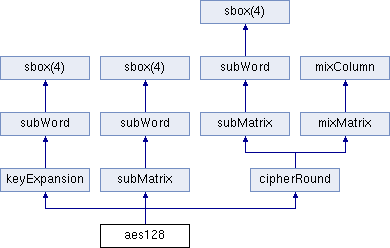

Fully Unrolled VHDL Implementation of AES-128

|

|

AES-128

1.0

Fully Unrolled VHDL Implementation of AES-128

|

High-throughput implementation of AES-128. More...

Entities | |

| Behavioral | architecture |

| Behavioral architecture of AES-128. More... | |

Libraries | |

| ieee | |

| work | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| ieee.numeric_std.all | |

| work.aes128Pkg.all | |

Ports | |

| Clk_CI | in std_logic |

| System clock. | |

| Reset_RBI | in std_logic |

| Synchronous, active-high reset. | |

| Start_SI | in std_logic |

| Starts the actual encryption process. | |

| NewCipherkey_SI | in std_logic |

| Determines whether a new cipherkey has been applied or not (i.e., whether the key expansion has to be performed or not). | |

| Busy_SO | out std_logic |

| Determines whether a the module is currently processing or not. | |

| Plaintext_DI | in std_logic_vector ( 127 downto 0 ) |

| The plaintext block to be encrypted. | |

| Cipherkey_DI | in std_logic_vector ( 127 downto 0 ) |

| the cipherkey to be used for encryption. | |

| Ciphertext_DO | out std_logic_vector ( 127 downto 0 ) |

| The resulting ciphertext. | |

High-throughput implementation of AES-128.

The present design implements the cipher of the 128-bit version of the Advanced Encryption Standard (AES). Since the design targets a high-throughput implementation, both the key expansion and the actual cipher are pipeline.

Inputs and outputs are registered. - While the plaintext and the ciphertext are registered in the top entity, the cipherkey is registered within the key expansion entity. Due to the input buffering, the actual encryption starts with a delay of one clock cycle. After that, both the key expansion and the encryption are executed "in parallel".

|

Port |

Determines whether a the module is currently processing or not.

| 0 | ... | Module is in IDLE mode. |

| 1 | ... | Module is currently encrypting. |

|

Port |

Determines whether a new cipherkey has been applied or not (i.e., whether the key expansion has to be performed or not).

| 0 | ... | No new cipherkey has been applied. |

| 1 | ... | A new cipherkey has been applied. |

|

Port |

Starts the actual encryption process.

| 0 | ... | Do not start the encryption. |

| 1 | ... | Start the encryption (value has to be applied only for a single clock cycle). |