|

AES-128

1.0

Fully Unrolled VHDL Implementation of AES-128

|

|

AES-128

1.0

Fully Unrolled VHDL Implementation of AES-128

|

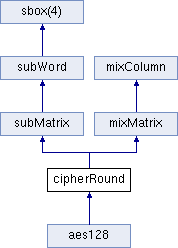

AES-128 single cipher round. More...

Entities | |

| Behavioral | architecture |

| Behavioral architecture description of a single AES round. More... | |

Libraries | |

| ieee | |

| work | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| work.aes128Pkg.all | |

Ports | |

| StateIn_DI | in Matrix |

| The internal state of AES being applied to this round. | |

| Roundkey_DI | in std_logic_vector ( 127 downto 0 ) |

| The roundkey to be used for the current AES round. | |

| StateOut_DO | out Matrix |

| The resulting state of AES after applying this round. | |

AES-128 single cipher round.

Implements a single cipher round of the AES-128 encryption algorithm, which can then be instantiated multiple times in order to create a high-throughput architecture.